Chiplet 并不是炒作

Imec 的 Eric Beyne 和 Geert Van der Plas 针对有些人认为 Chiplet是炒作现象的观点进行了如下回击:

Beyne 和 Van der Plas 写道,小芯片被《麻省理工学院技术评论》列为 2024 年十大突破性技术之一,已在半导体领域取得了重大进展。

芯片是小型模块化芯片,用于执行特定功能,例如 CPU 或 GPU,可以混合搭配成完整的系统。这种类似乐高积木的方法使制造商能够灵活地以低成本组合系统,降低新芯片设计的入门成本,提高效率和性能。

芯片实现优化的一种方法是通过战略性地定制技术。例如,IO 和总线芯片使用可靠的传统节点,而计算芯片则采用尖端技术以实现最佳性能。

内存芯片采用了新兴的内存技术,确保能够适应各种半导体需求。此外,基于芯片的设计加速了开发过程,因为过时的芯片可以轻松且更频繁地更新。

最后,芯片通常具有较高的成品率,因为它们通常更小、设计更简单,它们从经过预键合测试的已知良好的芯片开始,并且可以依靠修复策略来解决有缺陷的互连问题。

基于小芯片的设计解决了过去几十年来推动半导体行业发展的摩尔定律的放缓问题。为了确保集成电路上的元件数量每两年翻一番,芯片制造商探索了使晶体管更小、将更多元件塞入芯片的方法,从而产生了规模可观的单片系统级芯片 (SoC) 设计。

手机是单片设计成功的明证,它将数学函数、显示、无线通信、音频等全部集成到一块 100mm2芯片中 。然而,进一步的扩展成本非常高,性能优势却微乎其微。因此,我们的想法是将大型、复杂的 SoC 分成更小的芯片,并将它们连接在一起,为特定应用构建一个系统。

汽车行业是采用芯片的完美候选者,它提供灵活的电子架构,以基本功能芯片为基础,并添加特定组件,包括用于自动驾驶、传感器融合和其他电子功能的芯片。

模块化方法缩短了上市时间,在车辆生产线的整个生命周期内更换或更新芯片,而升级单片 SoC 则需要很长的过程。此外,汽车销售量(尤其是特定车型和类型的汽车)比手机等的销量要小。

因此,为每款车型重新设计单片 SoC(部分)将导致高昂的工程成本。最后,小芯片提供的灵活性还可以帮助汽车制造商使用已在其他汽车设计中得到验证的芯片来满足可靠性和安全性要求。

随着小芯片市场的发展,这些模块化设计预计将出现在更多的应用领域,如成像仪、显示器、存储器和量子计算。

图 1 - 芯片集提供一种模块化系统,它将来自不同供应商和技术节点的独立芯片组合在一起,而不是将所有功能设计到一个单片系统中。

芯片能否成功跟上摩尔定律,很大程度上取决于芯片在一个封装内能被放置得有多近,以确保它们之间快速、高带宽的电连接——就像单片 SoC 中的功能一样。

3D 系统集成领域正在出现两个主要的行业方向:通过公共基板(也称为中介层)将芯片并排连接的 2.5D 芯片集成和 3D-SoC,其中芯片彼此堆叠。

在 2.5D 集成中,芯片通过硅、有机聚合物、玻璃或层压板等公共基板连接。Imec 目前专注于硅和有机基板。虽然硅中介层是一种成熟的高性能应用技术,具有最精细的间距和良好的热电性能,但它们的成本和复杂性也更高。因此,有机基板作为替代方案得到了研究和优化。

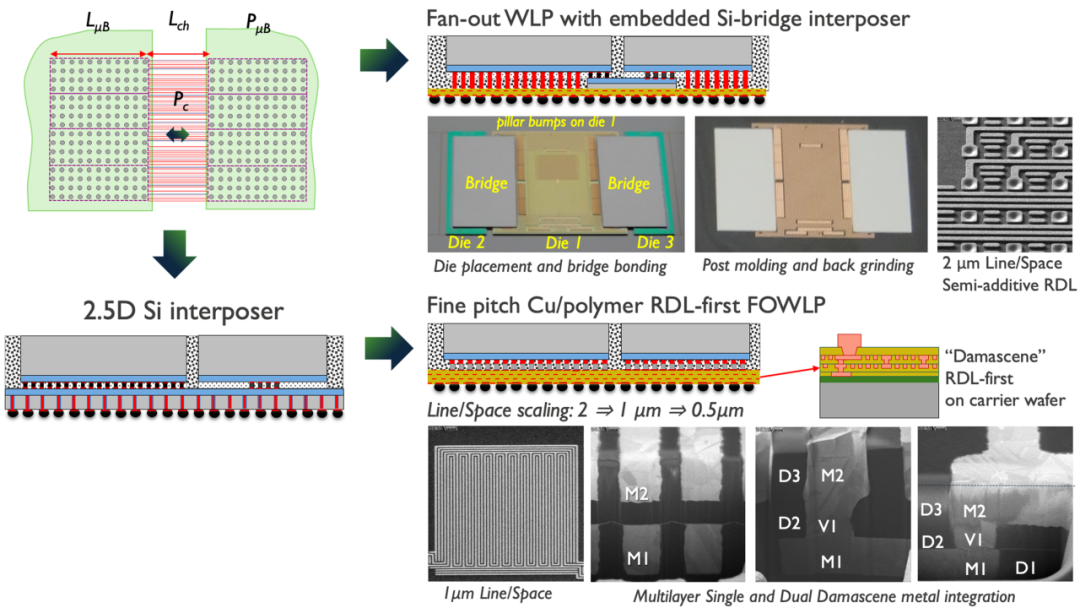

早期的芯片集成侧重于使用硅中介层基板进行芯片之间的互连。它涉及将两个独立的芯片非常紧密地(相距 <50μm)放置在公共中介层上,中介层是一种具有微米级布线的基板,用于建立连接。硅中介层利用传统的 BEOL Cu/氧化物镶嵌工艺来实现微米和亚微米级互连间距,且成品率非常高。

虽然这仍然是一种有效的方法,但替代技术正引起人们的兴趣,因为它们可能带来更具成本效益的解决方案。imec 提供的一种选择是硅“桥”,这是一种小型硅中介层,只将边缘处的芯片连接在一起。

另一种替代方案是超精细再分布层 (RDL)互连技术,该技术用有机聚合物代替硅,嵌入一层铜线以连接芯片。Imec 目前正在优化这项技术,致力于达到与硅同类产品类似的互连密度并提高与硅的兼容性。就间距而言,中介层仍以亚微米间距占据首位;imec 的目标是 RDL 间距达到 2微米,甚至在未来达到亚微米。

图 2 – 可以使用硅中介层集成芯片。Imec 还在研究硅桥或有机 RDL 等替代方案。

除了探索硅中介层技术的替代方案外,imec 还在研究如何通过增加额外功能使中介层成为更有价值的组件。例如,中介层可以有一个额外的去耦电容器,以保护芯片免受噪声和电源异常的影响。

某些应用(例如高性能计算)可能需要高性能、更小的外形尺寸或更高级别的系统集成度,因此更倾向于采用完整的 3D 方法。无需建立横向连接,芯片可以堆叠在一起,形成 3D-SoC。这种方法不会添加额外的模块,而是将芯片组合在一起进行设计,让它们像同一个芯片一样运行。

晶圆对晶圆混合键合是实现微米级互连密度 3D-SoC 集成的关键技术,它涉及将两个具有低温膨胀系数的硅芯片连接在一起。

此工艺中的关键部件是电介质,它可平坦化和激活堆叠层的表面以实现有效键合,并对堆叠中的不同芯片进行电绝缘。Imec 的专有方法将 SiCN 部署为键合电介质,将互连间距缩小至 700nm。路线图甚至预测间距为 400nm 和 200nm。

图 3 – 晶圆到晶圆混合键合是实现 3D-SoC 在 µm 级互连密度集成的关键技术。Imec 的专有方法使用 SiCN 作为键合电介质,可将互连间距缩小至 400nm。

对于 2.5D 技术,使用小焊料凸块将芯片放置在中介层顶部,从而建立电气和机械连接。这些微凸块之间的间距越细,连接就越快、越稳定。工业上的微凸块间距通常达到 50µm 到 30µm 之间。Imec 正在研究如何将间距减小到 10µm 甚至 5µm。

与 2.5D 中使用的微凸块相比,3D 堆叠中的混合键合产生的间距要小得多。那么,是否可以在任何地方使用混合键合?事实上,在芯片到晶圆的方法(基于硅)中,芯片可以键合到硅中介层,间距达到几微米。

不是 200nm,因为目前最佳的芯片到晶圆贴装精度接近 250nm,而尖端的晶圆到晶圆键合可以达到 100nm 的叠层精度。键合设备和相关工艺的改进有望进一步将这些数字降低 50%。不过,混合键合涉及额外的加工步骤,例如表面活化和对准,这可能会影响制造成本。

晶圆对晶圆键合、芯片对晶圆键合和微凸块将在成本、间距、兼容性和互操作性之间共存。在 2.5D 中,芯片通常来自不同的供应商,并且已经经过了一系列测试和操作。微凸块将成为首选,因为它们提供了一种不需要表面处理的标准化方法。此外,对于有机 RDL,微凸块仍然是首选,因为有机聚合物在加热时会膨胀得更多,并且无法充分平坦化。

随着规模技术变得越来越复杂,设计和处理成本也越来越高,对于小规模应用(想想汽车行业中大量的型号和类型)来说,在最先进的技术节点上开发专用 SoC 变得更具挑战性。

将功能和技术节点分成不同的芯片被证明更具成本效益,并且比尖端工艺技术中的巨型芯片具有空间和性能优势。

虽然模块化方法可以解决多芯片封装的复杂性和成本问题,但这种模式转变带来了特定的技术挑战。尺寸只是其中一个挑战。芯片研究的很大一部分致力于缩小互连尺寸和/或探索将各个部件组合在一起的不同概念。

当将芯片堆叠在一起时,散热问题和电力输送(通过背面电力输送网络等新架构解决)变得至关重要。最后,需要进一步的标准化工作,以确保不同芯片之间的兼容性和通信。

图 4 - imec 的 3D 互连路线图总结了互连芯片的不同方法以及预计的互连密度和间距。